CMOS라는 용어는 "상보적 금속 산화물 반도체"를 의미합니다. 이것은 컴퓨터 칩 설계 산업에서 가장 인기 있는 기술 중 하나이며 오늘날 수많은 다양한 응용 분야에서 집적 회로 를 형성하는 데 널리 사용됩니다 . 오늘날의 컴퓨터 메모리, CPU 및 휴대폰은 몇 가지 주요 이점으로 인해 이 기술을 사용합니다. 이 기술은 P 채널과 N 채널 반도체 소자를 모두 사용합니다. 오늘날 사용 가능한 가장 인기 있는 MOSFET 기술 중 하나는 상보형 MOS 또는 CMOS 기술입니다. 이것은 마이크로프로세서, 마이크로컨트롤러 칩, RAM, ROM, EEPROM과 같은 메모리 및 주문형 집적 회로(ASIC)를 위한 지배적인 반도체 기술입니다 .

MOS 기술 소개

IC 설계에서 가장 기본적이고 필수적인 구성 요소는 트랜지스터입니다. 따라서 MOSFET은 많은 응용 분야에서 사용되는 트랜지스터의 한 종류입니다. 이 트랜지스터의 형성은 반도체 층, 일반적으로 웨이퍼, 실리콘 단결정의 슬라이스; 이산화규소 층과 금속 층. 이들 층은 트랜지스터가 반도체 재료 내에 형성되도록 한다. Sio2와 같은 좋은 절연체는 100분자 두께의 얇은 층을 가지고 있습니다.

우리가 게이트 섹션에 금속 대신 다결정 실리콘(폴리)을 사용하는 트랜지스터. FET의 폴리실리콘 게이트는 대규모 IC에서 거의 금속 게이트를 사용하여 대체할 수 있습니다. 게이트 아래의 Sio2가 절연체이기 때문에 폴리실리콘 및 금속 FET를 모두 절연 게이트 FET를 의미하는 IGFET라고 하는 경우가 있습니다.

CMOS(상보성 금속 산화물 반도체)

NMOS 및 BIPOLAR 기술에 비해 CMOS 의 주요 이점은 훨씬 적은 전력 손실입니다. NMOS 또는 BIPOLAR 회로와 달리 보완 MOS 회로는 정적 전력 손실이 거의 없습니다. 회로가 실제로 전환되는 경우에만 전력이 소산됩니다. 이를 통해 NMOS 또는 바이폴라 기술 보다 IC에 더 많은 CMOS 게이트를 통합할 수 있으므로 훨씬 더 나은 성능을 얻을 수 있습니다. 상보형 금속 산화물 반도체 트랜지스터는 P-채널 MOS(PMOS)와 N-채널 MOS(NMOS)로 구성됩니다. CMOS 트랜지스터의 제조 공정에 대한 자세한 내용은 링크를 참조하십시오 .

CMOS(상보성 금속 산화물 반도체)

NMOS

NMOS는 n형 소스와 드레인이 확산된 p형 기판 위에 구축됩니다. NMOS에서 대부분의 캐리어는 전자입니다. 게이트에 높은 전압이 가해지면 NMOS가 전도됩니다. 마찬가지로 게이트에 낮은 전압이 가해지면 NMOS가 전도되지 않습니다. NMOS는 전자인 NMOS의 캐리어가 정공보다 두 배 빠른 속도로 이동하기 때문에 PMOS보다 빠른 것으로 간주됩니다.

NMOS 트랜지스터

PMOS

P-채널 MOSFET은 N-형 기판에 확산된 P-형 소스 및 드레인으로 구성됩니다. 대부분의 캐리어는 구멍입니다. 게이트에 고전압이 가해지면 PMOS가 전도되지 않습니다. 게이트에 낮은 전압이 가해지면 PMOS가 전도됩니다. PMOS 장치는 NMOS 장치보다 노이즈에 더 강합니다.

PMOS 트랜지스터

CMOS 작동 원리

CMOS 기술에서 N형 및 P형 트랜지스터는 논리 기능을 설계하는 데 사용됩니다. 한 유형의 트랜지스터를 켜는 동일한 신호가 다른 유형의 트랜지스터를 끄는 데 사용됩니다. 이 특성으로 인해 풀업 저항 없이 간단한 스위치만 사용하여 논리 장치를 설계할 수 있습니다.

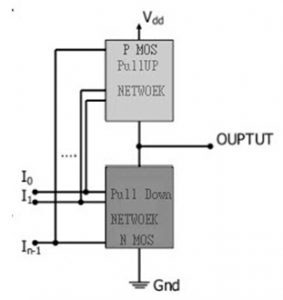

CMOS 로직 게이트 에서 n형 MOSFET 컬렉션은 출력과 저전압 전원 공급 장치 레일(Vss 또는 종종 접지) 사이의 풀다운 네트워크에 배열됩니다. NMOS 로직 게이트의 부하 저항 대신 CMOS 로직 게이트는 출력과 고전압 레일(종종 Vdd라고 함) 사이의 풀업 네트워크에 p형 MOSFET 모음을 가지고 있습니다.

풀업 및 풀다운을 사용하는 CMOS

따라서 p형 및 n형 트랜지스터의 게이트가 동일한 입력에 연결되어 있으면 n형 MOSFET이 꺼져 있을 때 p형 MOSFET이 켜지고 그 반대의 경우도 마찬가지입니다. 네트워크는 아래 그림과 같이 임의의 입력 패턴에 대해 하나는 ON이고 다른 하나는 OFF로 배열됩니다.

CMOS는 두 상태 모두에서 비교적 빠른 속도, 낮은 전력 손실, 높은 노이즈 마진을 제공하며 광범위한 소스 및 입력 전압에서 작동합니다(소스 전압이 고정된 경우). 또한, 상보성 금속 산화물 반도체의 작동 원리를 더 잘 이해하려면 아래에서 설명하는 CMOS 논리 게이트에 대해 간략히 설명해야 합니다.

어떤 장치가 CMOS를 사용합니까?

CMOS와 같은 기술은 마이크로컨트롤러, 마이크로프로세서, SRAM(정적 RAM) 및 기타 디지털 논리 회로와 같은 다양한 칩에 사용됩니다. 이 기술은 데이터 변환기, 이미지 센서 및 여러 종류의 통신을 위한 고도로 통합된 트랜시버를 포함하는 광범위한 아날로그 회로에 사용됩니다.

CMOS 인버터

인버터 회로는 아래 그림과 같습니다. PMOS와 NMOS FET 로 구성되어 있습니다 . 입력 A는 두 트랜지스터의 게이트 전압 역할을 합니다.

NMOS 트랜지스터는 Vss(접지)에서 입력을 받고 PMOS 트랜지스터는 Vdd에서 입력을 받습니다. 단자 Y가 출력됩니다. 인버터의 입력 단자(A)에 고전압(~ Vdd)이 주어지면 PMOS는 개방 회로가 되고 NMOS는 OFF되어 출력이 Vss로 풀다운됩니다.

CMOS 인버터

인버터에 낮은 수준의 전압(<Vdd, ~0v)이 인가되면 NMOS가 꺼지고 PMOS가 켜집니다. 따라서 출력이 Vdd가 되거나 회로가 Vdd로 풀업됩니다.

| 입력 | 논리 입력 | 산출 | 논리 출력 |

| 0V | 0 | Vdd | 1 |

| Vdd | 1 | 0V | 0 |

CMOS 낸드 게이트

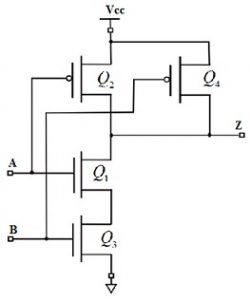

아래 그림은 2입력 Complementary MOS NAND 게이트를 보여줍니다. 이것은 Y와 접지 사이에 두 개의 직렬 NMOS 트랜지스터와 Y와 VDD 사이에 두 개의 병렬 PMOS 트랜지스터로 구성됩니다.

입력 A 또는 B가 논리 0이면 NMOS 트랜지스터 중 적어도 하나가 꺼져 Y에서 접지로의 경로가 차단됩니다. 그러나 pMOS 트랜지스터 중 적어도 하나는 ON이 되어 Y에서 VDD로의 경로를 생성합니다.

2입력 NAND 게이트

따라서 출력 Y는 높을 것입니다. 두 입력이 모두 높으면 nMOS 트랜지스터가 모두 ON이 되고 pMOS 트랜지스터가 모두 OFF가 됩니다. 따라서 출력은 로직 로우가 됩니다. 아래 표에 주어진 NAND 논리 게이트의 진리표.

| NS | NS | 풀다운 네트워크 | 풀업 네트워크 | 출력 Y |

| 0 | 0 | 끄다 | 에 | 1 |

| 0 | 1 | 끄다 | 에 | 1 |

| 1 | 0 | 끄다 | 에 | 1 |

| 1 | 1 | 에 | 끄다 | 0 |

CMOS NOR 게이트

2 입력 NOR 게이트는 아래 그림과 같습니다. NMOS 트랜지스터는 입력 중 하나가 높을 때 출력을 낮추기 위해 병렬입니다. PMOS 트랜지스터는 아래 표와 같이 두 입력이 모두 낮을 때 출력을 높게 끌어오기 위해 직렬입니다. 출력은 부동 상태로 남아 있지 않습니다.

2입력 NOR 게이트

아래 표에 주어진 NOR 논리 게이트의 진리표.

| NS | NS | 와이 |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |